| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

Tags

- Machine Learning

- PCA

- 오블완

- LG

- 회귀

- GPT-4

- 머신러닝

- 티스토리챌린지

- LG Aimers 4th

- Classification

- regression

- 분류

- OpenAI

- 딥러닝

- ChatGPT

- supervised learning

- 해커톤

- gpt

- LLM

- LG Aimers

- AI

- deep learning

- 지도학습

Archives

- Today

- Total

SYDev

[컴퓨터 구조] Lecture 15: The Processor - Part4 본문

경희대학교 김정욱 교수님의 컴퓨터 구조 강의 내용을 기반으로 한 정리글

Pipeline Hazards

- 파이프라이닝 -> 속도 향상 -> 향상된 성능

- 그러나 3가지 Hazards 발생

- Structure hazards

- Data hazards

- Control hazards

Structure Hazards

- 자원 충돌로 인해서 발생

- 하드웨어가 같은 clock cycle 내에서 우리가 원하는 명령어의 조합을 실행할 수 없는 문제

- 문제) 명령어와 데이터가 같은 메모리에 저장된 경우 -> fetch, memory 단계가 같은 clock cycle에 겹치면, 같은 메모리에 동시에 접근하여 충돌 발생

solution 1: stall(한 사이클 중지)

-> 하지만 이 경우 다음, 그 다음 clock cycle과 겹치는 경우 발생

solution 2: 명령어 메모리와 데이터 메모리를 나누는 방법

Data Hazard

- 이전 명령어의 wb이 반영되기 이전에 다음 명령어(wb 반영될 예정인 레지스터 포함)의 exe가 실행되는 경우 발생

- pipeline 구조에서 r format의 rd값이 다음 명령어의 rs 혹은 rt에 위치할 때 문제가 발생

-> 아직 wb이 반영되지 않았는데 2번째 명령어의 exe가 진행됨

Naive solution 1: 휴식

그러나, 이렇게 될 경우 싱글 사이클과 별 차이가 없게 됨

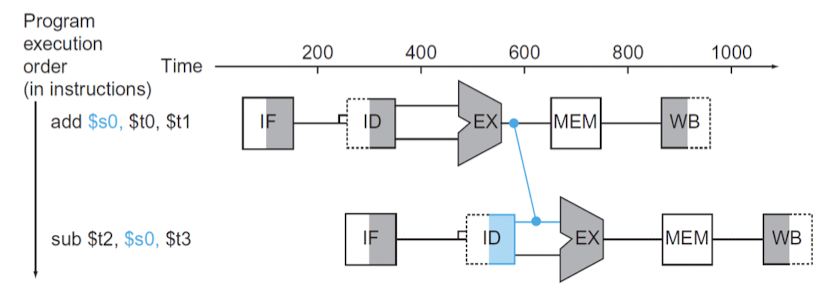

Primary solution: Forwarding or Bypassing

- 쉬어갈 필요 없이, exe 단계에서 나온 wb될 값을 미리 다음 명령어로 넘겨준다. (그렇다고 wb되는 것은 아님)

-> $1에 wb될 값을 미리 넘겨주지만, cc5에서 wb이 적용되기 전까지는 $1값은 바뀌지 않음

-> $s0가 rs에 위치하면 위의 선, rt에 위치하면 아래 선

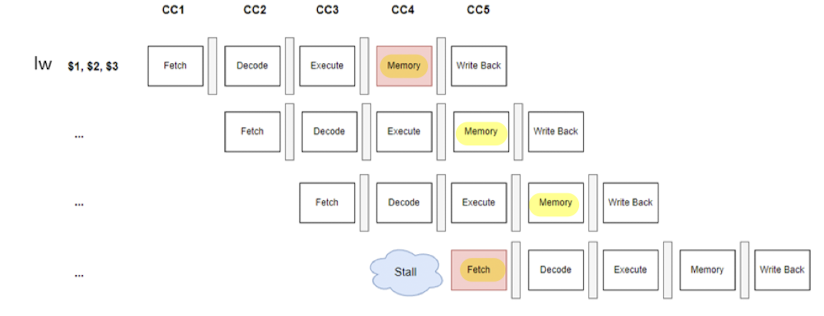

Load-use data Hazard

- lw 명령어의 $s0가 다음 명령어에서 사용될 때, 한 스테이지만큼 쉼으로써 문제를 해결한다.

solution: Reordering -> to avoid pipeline stalls

-> 좌측의 경우에는 $t2에 lw하는 명령어 바로 뒤의 add 연산이 $t2를 사용하기 때문에 한 번의 stall, $t4에 lw하는 명령어 바로 뒤의 add 연산이 $t4를 사용하기 때문에 또 한 번의 stall이 발생한다.

-> 명령어 순서를 적절히 재배치하여 지연을 최소화한다.

-> sub 명령어의 exe/mem에서 2번째 명령어로, mem/wb에서 3번째 명령어로 forwarding해줘야 한다.

Notation of data hazard conditions

- Format: AA/BB.RegisterRd = CC/DD.RegisterRs or CC/DD.RegisterRt

- ex) ID/EX.RegisterRs: ID/EX에서 발견되는 레지스터 Rs 번호

- 1a. EX/MEM.RegisterRd = ID/EX.RegisterRs -> EX/MEM단계의 rd가 ID/EX(다음 명령어)단계의 rs와 같으면 1a hazard

- 1b. EX/MEM.RegisterRd = ID/EX.RegisterRt -> EX/MEM단계의 rd가 ID/EX(다음 명령어)단계의 rt와 같으면 1b hazard

- 2a. MEM/WB.RegisterRd = ID/EX.RegisterRs -> MEM/WB 단계의 rd가 ID/EX(다다음 명령어)단계의 rs와 같으면 2a hazard

- 2b. MEM/WB.RegisterRd = ID/EX.RegisterRs -> MEM/WB 단계의 rd가 ID/EX(다다음 명령어)단계의 rt와 같으면 2b hazard

-> 이 조건이 만족하면 바로 forwarding 수행

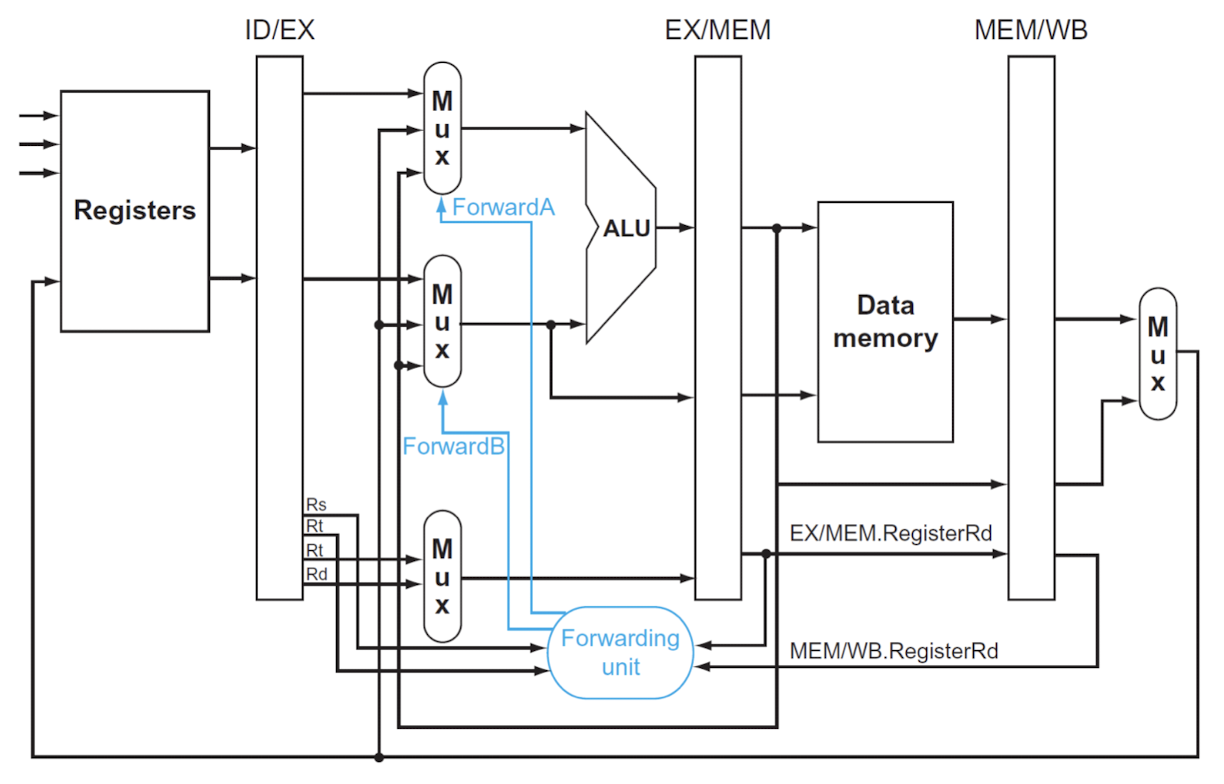

Fowarding

- EX/MEM.RegisterRd와 MEM/WB.RegisterRd, ID/EX의 Rs, Rt 값을 보고 Forwarding을 결정

Detecting data hazards

EX hazard

//R-format에서 현재 EX/MEM의 Rd가 다음 단계 명령어의 ID/EX Rs와 같다면 포워딩

//forwardA

if (EX/MEM.RegWrite and //R-format 혹은 lw

and (EX/MEM.RegisterRd != 0) //Rd 값이 유효하다 -> lw가 아님

and (EX/MEM.RegisterRd == ID/EX.RegisterRs)) ForwardA = 10;

//forwardB

if (EX/MEM.RegWrite and //R-format 혹은 lw

and (EX/MEM.RegisterRd != 0) //Rd 값이 유효하다 -> lw가 아님

and (EX/MEM.RegisterRd == ID/EX.RegisterRt)) Forward = 10;

MEM hazard

//2a hazard

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd != 0)

and (MEM/WB.RegisterRd == ID/EX.RegisterRs)) ForwardA = 01;

//2b hazard

if (MEM/WB.ReWrite

and (MEM/WB.RegisterRd != 0)

and (MEM/WB.RegisterRd == ID/EX.RegisterRt)) ForwardB = 01;

Additional case

- MEM hazard를 고려할 때, 중간 라인에 rd값이 포함된 경우도 고려해야 함

//2a hazard

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd != 0)

and not(EX/MEM.RegWrite and (EX/MEM.RegisterRd != 0)

and (EX/MEM.RegisterRd == ID/EX.RegisterRs))

and (MEM/WB.RegisterRd == ID/EX.RegisterRs)) ForwardA = 01;

//2b hazard

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd != 0)

and not(EX/MEM.RegWrite and (EX/MEM.RegisterRd != 0)

and (EX/MEM.RegisterRd == ID/EX.RegisterRt))

and (MEM/WB.RegisterRd == ID/EX.RegisterRt)) ForwardB = 01;

최종 Data Hazard 회로

Load-use Data Hazards

- lw의 rd를 다음 명령어의 rs 혹은 rt가 포함하고 있는 경우

if (ID/EX.MemRead and // ID/EX의 MemRead를 읽고 있는 상태 -> 현재 instruction이 lw 다음에 수행

((ID/EX.RegisterRt == IF/ID.RegisterRs) or

(ID/EX.RegisterRt = IF/ID.RegisterRt))) // lw의 목적지(Rt)가 현재 R-format 연산이 수행되어야 하는 Rs 혹은 Rt에 대응되는지 확인

stall the pipeline; // 조건이 만족하면 stall-> ID/EX, IF/ID 대신 EX/IM, ID/EX로 설정해두면, problem을 인식하고 stall하기에 늦어버림

-> 때문에 한 단계 전에서 수행

Checking for load instructions

- stall하는 방법 -> Insert nop(no operation)

- nop: 상태를 바꾸는 연산을 진행하지 않는 명령어

Pipeline control overview

728x90

반응형

'3학년 1학기 전공 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Lecture 17: Memory Hierarchy - Part1 (7) | 2024.06.03 |

|---|---|

| [컴퓨터 구조] Lecture 16: The Processor - Part5 (0) | 2024.05.31 |

| [컴퓨터 구조] Lecture 14: The Processor - Part3 (0) | 2024.05.20 |

| [컴퓨터 구조] Lecture 13: The Processor - Part2 (0) | 2024.05.20 |

| [컴퓨터 구조] Lecture 12: The Processor (0) | 2024.05.05 |